High-Speed Serial Interface (HSSI)

Simulation Objectives

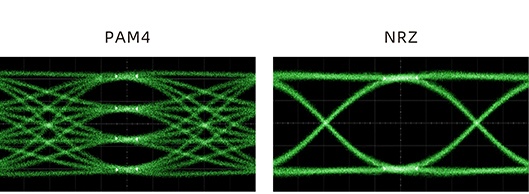

PCIE5, SATA, SAS, SFP28, 10GBase-KR, 100GBase-KR4, 56G/112G/224G PAM4 and other high-speed serial signals

Simulation Difficulties

Impedance mismatch,excessive loss, serious ISI

Simulation Process

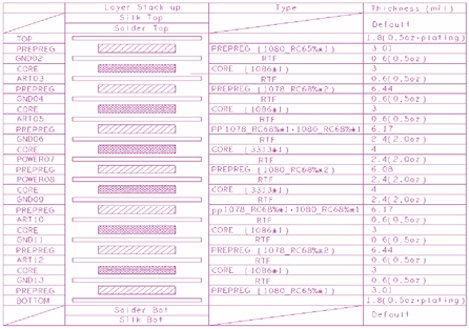

Cascade Design

Plan the lamination according to the actual situation, comprehensively consider the model, thickness, glue content, glue flow rate, etc. of the semi-cured sheet/core board, and provide reasonable impedance control, wiring layer/power ground plane planning and other suggestions.

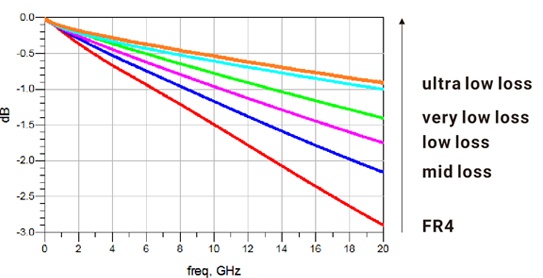

Plate Selection

According to the system signal type and channel conditions, select the plate reasonably to ensure the signal quality and reduce the production cost.

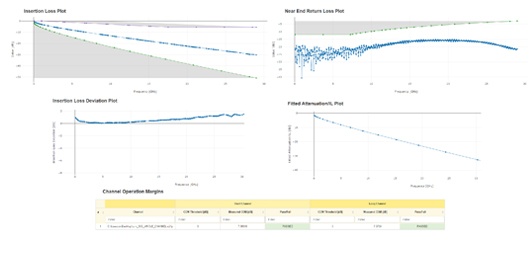

Passive Channel Evaluation Based on S Parameter

Determine whether the channel conforms to the protocol standard through the S parameter, and analyze the details of the channel to ensure the system performance.

Active Simulation Based on HSPICE/AMI Model

Add a specific rate code type for eye graph simulation

Measured by eye height and eye width